WD4000國產(chǎn)晶圓幾何形貌量測設(shè)備通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV、BOW、WARP、在高效測量測同時有效防止晶圓產(chǎn)生劃痕缺陷。可實現(xiàn)砷化鎵

2024-03-15 09:22:08

立錡推出的低壓輸入、CSP 小封裝降壓轉(zhuǎn)換器系列,不僅滿足各式小型穿戴式和 IoT 物聯(lián)網(wǎng)應用的需求,更在性能和尺寸上取得了絕佳平衡。

2024-03-14 15:03:10 189

189 面對晶振頻差不一樣的情況時,需要滿足以下條件才能進行替換:

1.頻率范圍:新晶振的頻率范圍必須覆蓋舊晶振的頻率范圍。如果新晶振的頻率范圍過窄,可能無法滿足設(shè)備的需求。

2. 封裝尺寸:新晶振的封裝尺寸

2024-03-04 13:48:39

WD4000無圖晶圓幾何形貌測量系統(tǒng)是通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產(chǎn)生劃痕缺陷。可兼容不同材質(zhì)

2024-02-21 13:50:34

WD4000無圖晶圓幾何形貌測量設(shè)備采用高精度光譜共焦傳感技術(shù)、光干涉雙向掃描技術(shù),完成非接觸式掃描并建立3D Mapping圖,實現(xiàn)晶圓厚度、TTV、LTV、Bow、Warp、TIR、SORI、等

2024-01-10 11:10:39

WD4000半導體晶圓厚度測量系統(tǒng)自動測量Wafer厚度、表面粗糙度、三維形貌、單層膜厚、多層膜厚。1、使用光譜共焦對射技術(shù)測量晶圓Thickness、TTV、LTV、BOW、WARP、TIR

2024-01-09 09:08:07

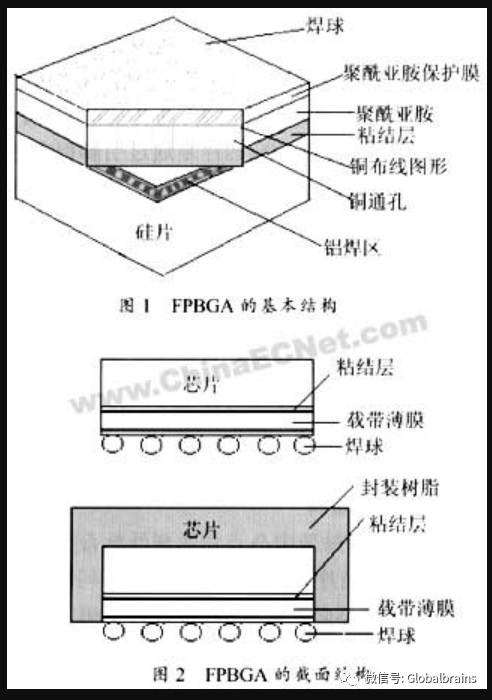

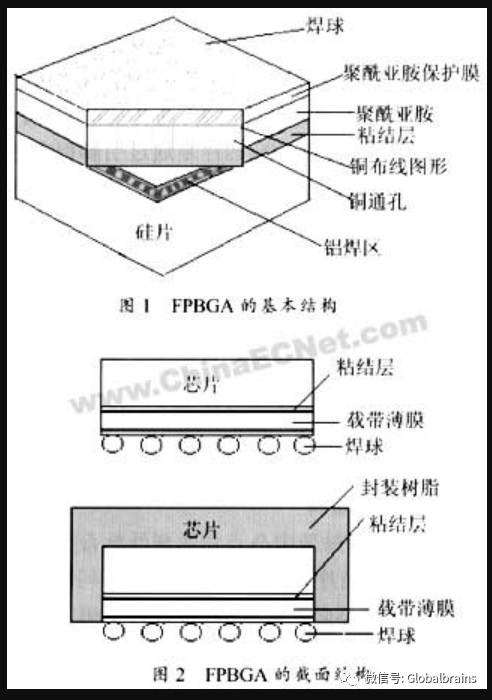

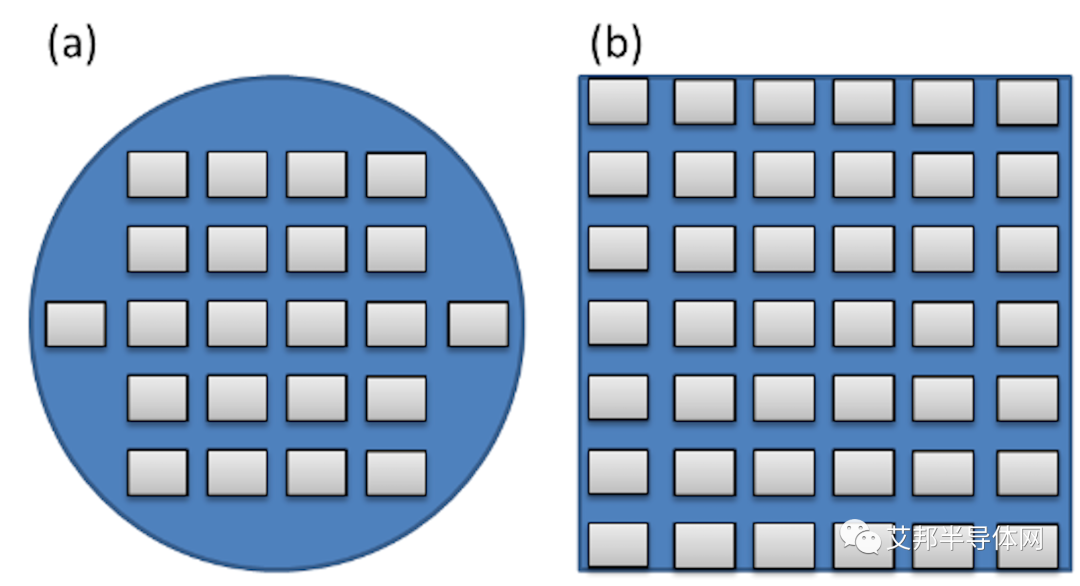

為了實現(xiàn)集成電路芯片的電通路,一般需要將芯片裝配到在塑料或陶瓷載體上,這一過程可以稱為CSP。CSP的尺寸只是略大于芯片,通常封裝尺寸不大于芯片面積的1.5倍或不大于芯片寬度或長度的?1.2

2023-12-22 09:08:31 534

534

TC-Wafer是將高精度溫度傳感器鑲嵌在晶圓表面,對晶圓表面的溫度進行實時測量。通過晶圓的測溫點了解特定位置晶圓的真實溫度,以及晶圓整體的溫度分布,同還可以監(jiān)控半導體設(shè)備控溫過程中晶圓發(fā)生的溫度

2023-12-21 08:58:53

)及分析反映表面質(zhì)量的2D、3D參數(shù)。廣泛應用于襯底制造、晶圓制造、及封裝工藝檢測、3C電子玻璃屏及其精密配件、光學加工、顯示面板、MEMS器件等超精密加工行業(yè)。WD

2023-12-20 11:22:44

以來迅速發(fā)展的新型微電子封裝技術(shù),包括焊球陣列封裝(BGA)、芯片尺寸封裝(CSP)、圓片級封裝(WLP)、三維封裝(3D)和系統(tǒng)封裝(SIP)等項技術(shù)。介紹它們的發(fā)展狀況和技術(shù)特點。同時,敘述了微電子

2023-12-11 01:02:56

、ATX-H12和ATX-H13溫補晶振(TCXO)系列特別適用于具有Wi-Fi、GPS和藍牙服務的空間受限和功率受限的設(shè)備。這些設(shè)備為需要電信、導航和定位等功能的精確定時解決方案的應用提供了低至±2ppm的緊密

2023-12-07 09:30:19

國產(chǎn)有哪些FPGA入門?萊迪思半導體?高云半導體?

2023-12-05 16:05:38

晶圓測溫系統(tǒng)tc wafer晶圓表面溫度均勻性測溫晶圓表面溫度均勻性測試的重要性及方法 在半導體制造過程中,晶圓的表面溫度均勻性是一個重要的參數(shù)

2023-12-04 11:36:42

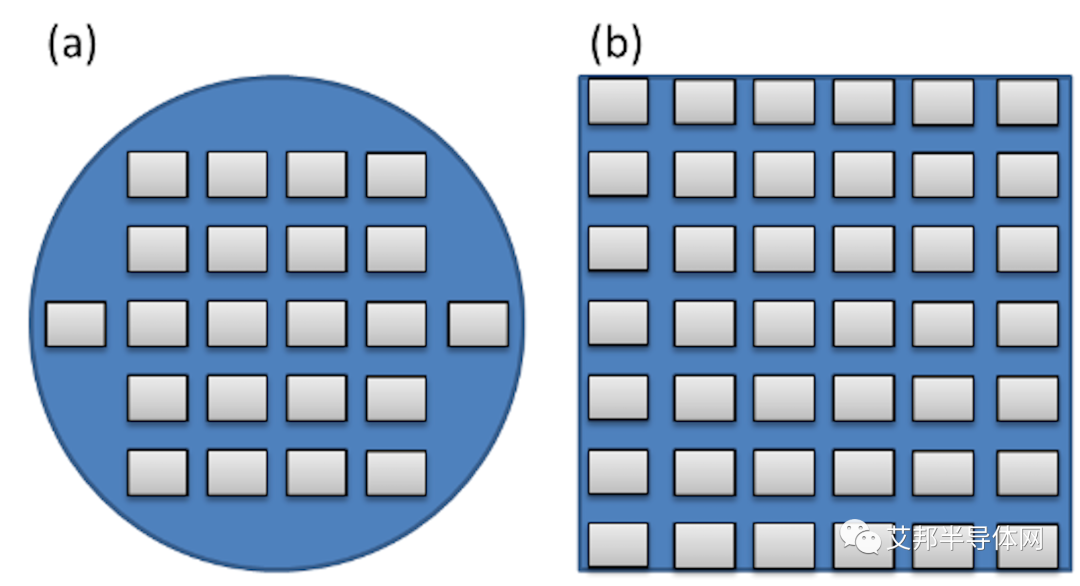

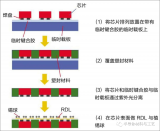

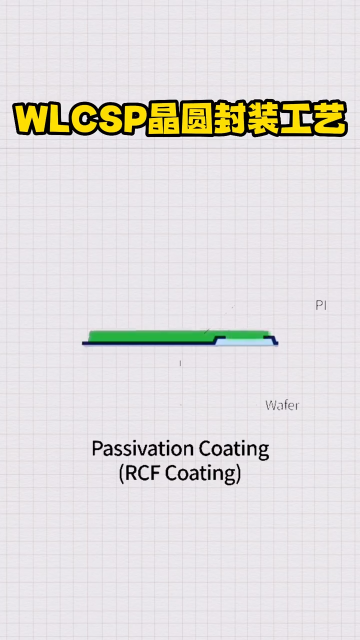

半導體封裝方法,大致可以分為兩種:傳統(tǒng)封裝和晶圓級(Wafer-Level)封裝。傳統(tǒng)封裝首先將晶圓切割成芯片,然后對芯片進行封裝;而晶圓級封裝則是先在晶圓上進行部分或全部封裝,之后再將其切割成單件。

2023-11-19 12:30:08 1014

1014 三星計劃在2024年先進3D芯片封裝技術(shù)SAINT(Samsung Advanced Interconnection Technology,三星高級互連技術(shù)),能以更小尺寸的封裝,將AI芯片等高性能芯片的內(nèi)存和處理器集成。

2023-11-15 11:09:30 931

931 請問像AD8233一樣的晶圓封裝在PCB中如何布線,芯片太小,過孔和線路都無法布入,或者有沒有其他封裝的AD8233

2023-11-14 07:01:48

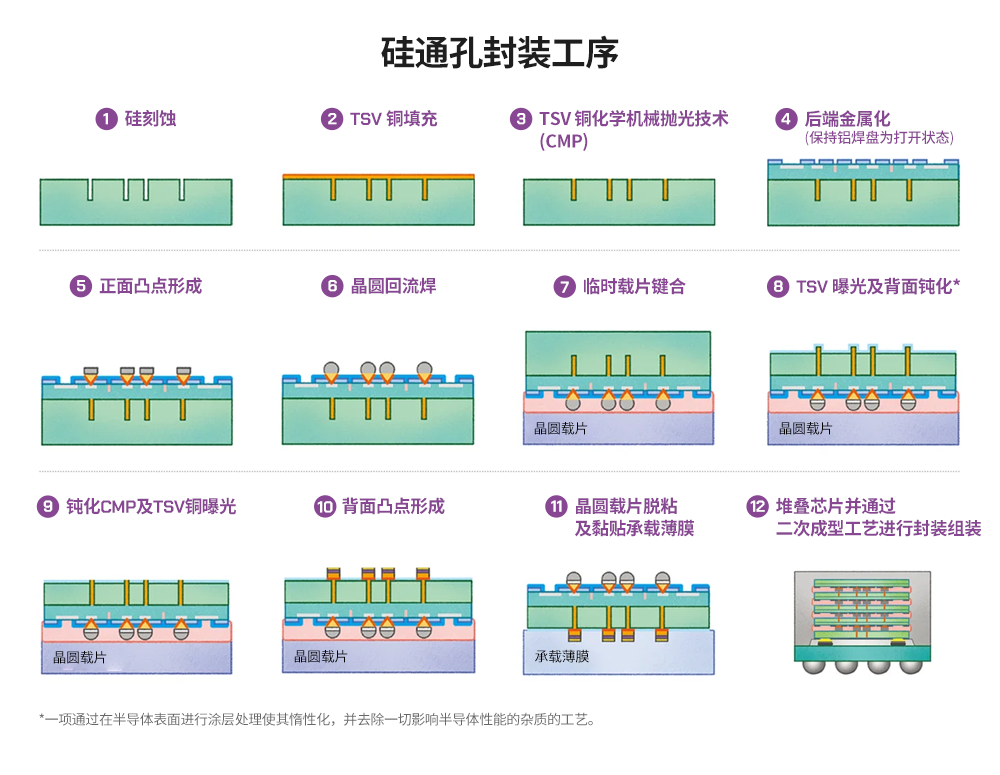

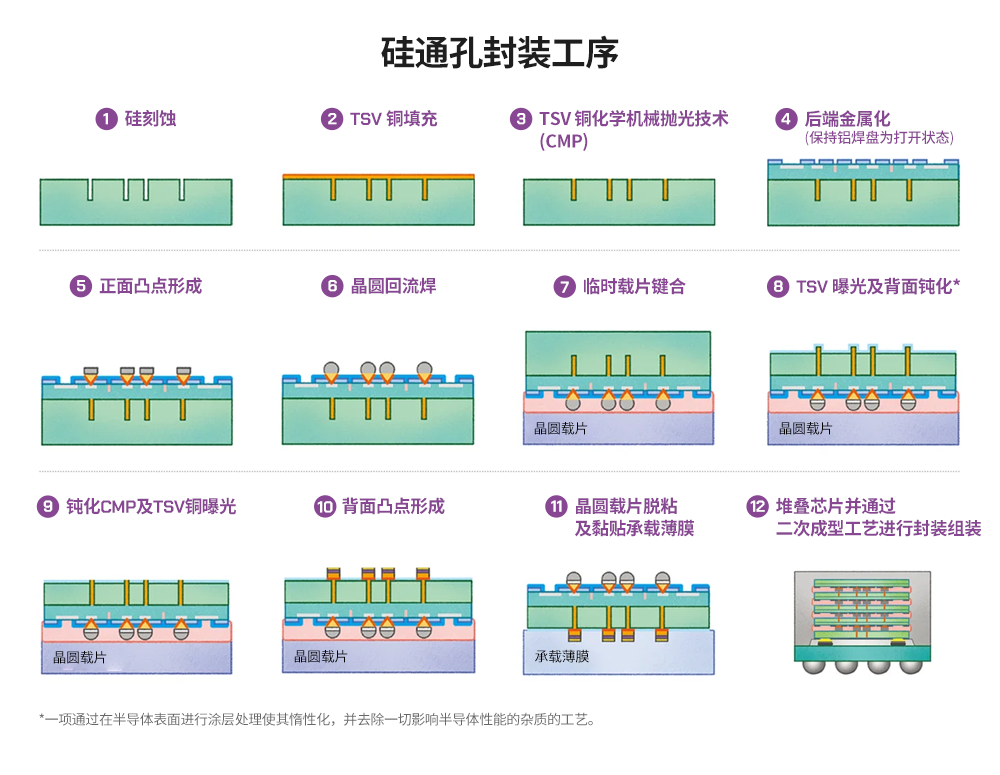

在上篇文章中介紹了扇入型晶圓級芯片封裝(Fan-In WLCSP)、扇出型晶圓級芯片封裝(Fan-Out WLCSP)、重新分配層(RDL)封裝、倒片(Flip Chip)封裝,這篇文章著重介紹硅通孔(TSV)封裝工藝。

2023-11-08 10:05:53 1825

1825

介紹了晶圓級封裝的基本流程。本篇文章將側(cè)重介紹不同晶圓級封裝方法所涉及的各項工藝。晶圓級封裝可分為扇入型晶圓級芯片封裝(Fan-In WLCSP)、扇出型晶圓級芯片封裝(Fan-Out WLCSP

2023-11-08 09:20:19 2746

2746

WLCSP(Wafer Level Chip Scale Packaging)即晶圓級芯片封裝方式,不同于傳統(tǒng)的芯片封裝方式(先切割再封測,而封裝后至少增加原芯片20%的體積),此種最新技術(shù)是先在整片晶圓上進行封裝和測試,然后才切割成一個個的IC顆粒,因此封裝后的體積即等同IC裸晶的原尺寸。

2023-11-06 11:02:07 1026

1026

WD4000晶圓幾何形貌測量及參數(shù)自動檢測機通過非接觸測量,將晶圓的三維形貌進行重建,強大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產(chǎn)生劃痕缺陷

2023-11-06 10:49:18

WD4000系列半導體晶圓幾何形貌自動檢測機采用高精度光譜共焦傳感技術(shù)、光干涉雙向掃描技術(shù),完成非接觸式掃描并建立3D Mapping圖,實現(xiàn)晶圓厚度、TTV、LTV、Bow、Warp、TIR

2023-11-06 10:47:07

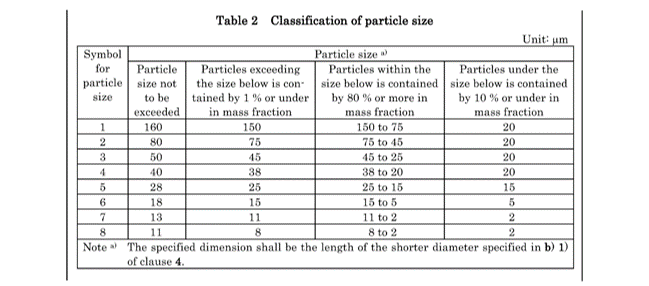

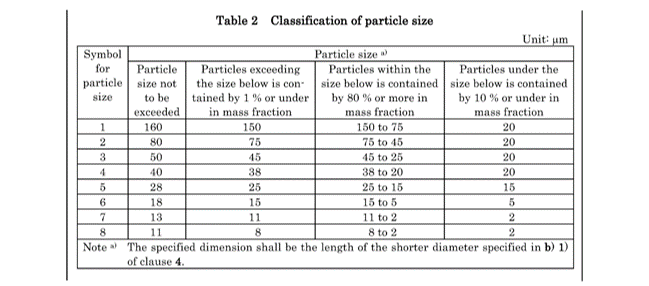

介紹微型芯片封裝如何選擇合適的焊粉尺寸?

2023-10-27 10:17:40 207

207

WD4000半導體晶圓表面三維形貌測量設(shè)備自動測量Wafer厚度、表面粗糙度、三維形貌、單層膜厚、多層膜厚。可廣泛應用于襯底制造、晶圓制造、及封裝工藝檢測、3C電子玻璃屏及其精密配件、光學加工、顯示

2023-10-23 11:05:50

WD4000半導體晶圓檢測設(shè)備自動測量Wafer厚度、表面粗糙度、三維形貌、單層膜厚、多層膜厚。1、使用光譜共焦對射技術(shù)測量晶圓Thickness、TTV、LTV、BOW、WARP、TIR、SORI

2023-10-19 11:08:24

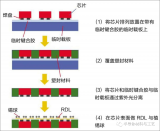

晶圓級封裝是指晶圓切割前的工藝。晶圓級封裝分為扇入型晶圓級芯片封裝(Fan-In WLCSP)和扇出型晶圓級芯片封裝(Fan-Out WLCSP),其特點是在整個封裝過程中,晶圓始終保持完整。

2023-10-18 09:31:05 1339

1339

WD4000無圖晶圓幾何量測系統(tǒng)自動測量 Wafer 厚度 、表面粗糙度 、三維形貌 、單層膜厚 、多層膜厚 。使用光譜共焦對射技術(shù)測量晶圓 Thickness 、TTV 、LTV 、BOW

2023-10-18 09:09:00

麒麟a2芯片尺寸是多少 麒麟a2芯片尺寸是多少這個問題目前沒有相關(guān)官方的報道,因此無法給出準確的回答。麒麟A2是華為旗下的音頻芯片,麒麟A2芯片功耗相比上一代直接降低了50%,真正實現(xiàn)了高性能

2023-10-17 16:20:31 930

930 MINI USB接口尺寸封裝集合

2023-09-28 07:16:45

扇出型晶圓級封裝技術(shù)采取在芯片尺寸以外的區(qū)域做I/O接點的布線設(shè)計,提高I/O接點數(shù)量。采用RDL工藝讓芯片可以使用的布線區(qū)域增加,充分利用到芯片的有效面積,達到降低成本的目的。扇出型封裝技術(shù)完成芯片錫球連接后,不需要使用封裝載板便可直接焊接在印刷線路板上,這樣可以縮短信號傳輸距離,提高電學性能。

2023-09-25 09:38:05 756

756

定義:它是在基板的下邊按面陣方式引出球形引腳,在基板上面貼裝LSI芯片,是LSI芯片常用的-種表面貼裝型封裝形式。

2023-09-22 10:49:27 1176

1176

電子發(fā)燒友網(wǎng)站提供《32位單片機晶圓級芯片尺寸封裝(WLCSP).pdf》資料免費下載

2023-09-19 16:12:26 0

0 電子發(fā)燒友網(wǎng)站提供《32位單片機晶圓級芯片尺寸封裝(WLCSP).pdf》資料免費下載

2023-09-19 14:23:37 0

0 器件制造具有以下優(yōu)點[1]

(1) 片子平面的總體平面度: CMP 工藝可補償亞微米光刻中步進機大像場的線焦深不足。

(2) 改善金屬臺階覆蓋及其相關(guān)的可靠性: CMP工藝顯著地提高了芯片測試中的圓片成品率。

(3) 使更小的芯片尺寸增加層數(shù)成為可能: CMP技術(shù)允許所形成的器件具有更高的縱橫比。

2023-09-19 07:23:03

01CW24x系列串行EEPROM具有低引腳數(shù)、高可靠性、多種存儲容量用于靈活的參數(shù)管理和小代碼存儲,滿足穩(wěn)定的數(shù)據(jù)保存、低功耗和空

02間受限的需要

03采用華虹95nm最先進工藝,晶圓CP測試

2023-09-15 08:22:26

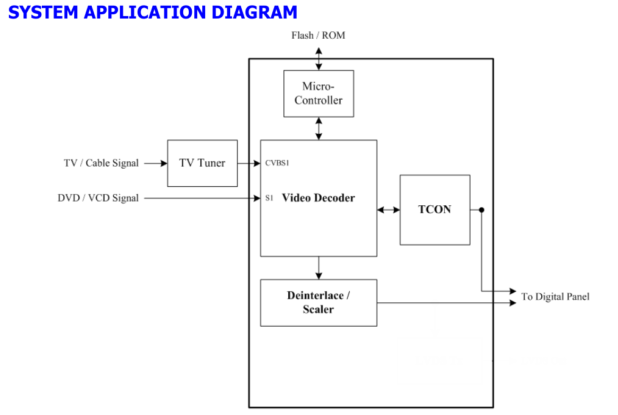

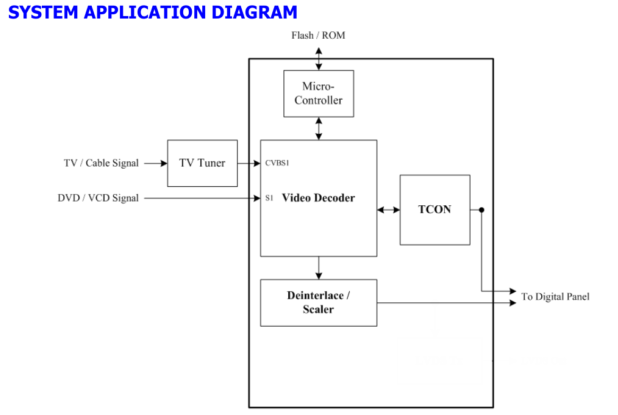

SSD101是SigmaStar推出的用于驅(qū)動小尺寸TTL-RGB接口液晶屏的方案,價格在10元人民幣左右,性價比非常高,一般應用于車載顯示驅(qū)動,可視門鈴,以及一些只需要CVBS(AV)輸入的驅(qū)動小尺寸液晶顯示產(chǎn)品中,芯片尺寸小,只有64個腳,功耗低,還可以電池供電。

2023-09-13 15:19:23 994

994

所謂芯片尺寸封裝就是CSP (Chip Size Package或Chip Scale Package)。JEDEC(美國EIA協(xié)會聯(lián)合電子器件工程委員會)的JSTK一012標準規(guī)定,LSI芯片封裝

2023-09-06 11:14:55 565

565

PFA花籃(PFA wafer Cassette) 又名 清洗花藍 ,鐵氟龍卡匣 , 鐵氟龍晶舟盒 ,鐵氟龍晶圓盒為承載半導體晶圓片/硅片

2023-08-29 08:57:51

DA14580 DEVKT -Pro 子板 WLCSP34 Electrical 原理圖

2023-07-06 19:41:40 0

0 PLD是可編程邏輯器件(Programmable Logic Device)的縮寫。它是一種集成電路芯片,具有可編程的邏輯功能。PLD可以根據(jù)用戶需求進行編程,實現(xiàn)特定的邏輯功能和電路設(shè)計。

2023-07-05 15:50:35 2551

2551 晶圓測溫系統(tǒng),晶圓測溫熱電偶,晶圓測溫裝置一、引言隨著半導體技術(shù)的不斷發(fā)展,晶圓制造工藝對溫度控制的要求越來越高。熱電偶作為一種常用的溫度測量設(shè)備,在晶圓制造中具有重要的應用價值。本文

2023-06-30 14:57:40

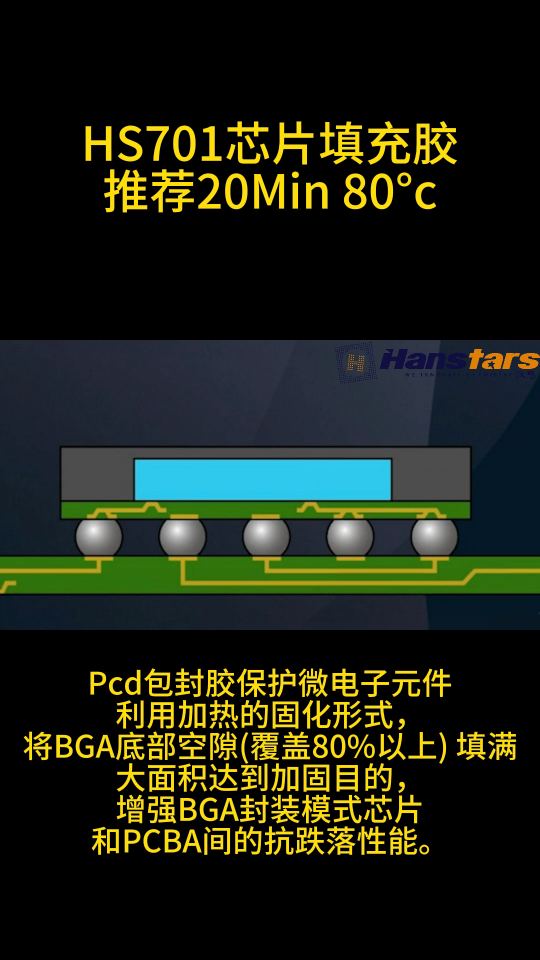

射頻電子標簽qfn芯片封裝用底部填充膠由漢思新材料提供客戶產(chǎn)品:射頻電子標簽。目前用膠點:qfn芯片加固。芯片尺寸:0.8MM*1.3MM客戶要求:目前客戶可以接受加熱。顏色目前暫時沒有要求

2023-06-30 14:01:42 553

553

PLD系列準分子激光器采用不同激光介質(zhì),如氣體、液體或固體。通過在介質(zhì)中產(chǎn)生激發(fā)態(tài)粒子,然后通過受激輻射過程產(chǎn)生激光。

2023-06-29 11:28:03 287

287

不同封裝的晶振,有什么差別沒有

2023-06-26 06:09:47

今天我們來介紹PLCSP(Panel Level Chip Scale Packaging)。同理,PLCSP是一種將面板級封裝(PLP)和芯片尺寸封裝(CSP)合為一體的封裝技術(shù)。芯片尺寸封裝(CSP)是指整個package的面積相比于silicon總面積不超過120%的封裝技術(shù)。

2023-06-19 11:31:46 864

864

在計算焊盤坐標時,數(shù)據(jù)手冊中指定的芯片尺寸與從晶圓上切割后的物理芯片尺寸之間經(jīng)常存在混淆。芯片的物理邊緣不是引線鍵合的良好參考,因為整體芯片尺寸略有不一致。本應用筆記將簡要討論芯片尺寸、芯片方向、鍵合坐標以及如何計算物理芯片尺寸。MAX3970將作為示例。

2023-06-16 17:23:19 370

370 ①須包括以下參數(shù):管腳間距、芯片尺寸、厚度等;

②測試的參數(shù)指標:溫度、頻率、電流、電壓的等;

2023-06-13 09:17:30 427

427

芯片功能測試常用5種方法有板級測試、晶圓CP測試、封裝后成品FT測試、系統(tǒng)級SLT測試、可靠性測試。

2023-06-09 16:25:42

從理論上講,環(huán)形電感器的封裝尺寸可以是多種多樣的,不同電性能的環(huán)形電感器的封裝尺寸也可以是相同的。目前,市場上常規(guī)的環(huán)形電感器的包裝尺寸相對固定。當然,這里提到的固定不僅僅意味著單個封裝尺寸,而是具有相同電性能的環(huán)形電感器的封裝尺寸基本相同。一般來說,制造商不太可能調(diào)整常規(guī)環(huán)形電感器封裝尺寸。

2023-05-26 16:26:35 2

2 我們正在開發(fā)基于 imx8mp 處理器的產(chǎn)品。它通過 i2c 總線將程序加載到萊迪思 CrossLink FPGA。FPGA 二進制數(shù)據(jù)大小(.ied 文件)為 149KB,使用 400 KHz

2023-05-16 06:28:53

控制與安全,是萊迪思(Lattice)MachXO系列FPGA最鮮明的“標簽”。從側(cè)重于控制功能的MachXO/MachXO2/MachXO3,到行業(yè)第一顆安全控制FPGA芯片MachXO3D和具備

2023-05-12 09:45:04 719

719

半導體大規(guī)模生產(chǎn)過程中需要在晶圓上沉積集成電路芯片,然后再分割成各個單元,最后再進行封裝和焊接,因此對晶圓切割槽尺寸進行精準控制和測量,是生產(chǎn)工藝中至關(guān)重要的環(huán)節(jié)。

2023-05-09 14:12:38

先進物聯(lián)網(wǎng)解決方案的領(lǐng)先供應商橙群微電子,很高興地宣布,其獲獎的NanoBeaconSoCIN100采用突破性的晶圓級芯片規(guī)模封裝(WLCSP)。這種新的封裝尺寸

2023-05-09 11:43:56 983

983

? 先進物聯(lián)網(wǎng)解決方案的領(lǐng)先供應商橙群微電子,很高興地宣布,其獲獎的NanoBeacon SoC IN100采用突破性的晶圓級芯片規(guī)模封裝(WLCSP)。這種新的封裝尺寸為1.1mm x 2.0mm

2023-05-09 09:56:58 408

408

圓片級芯片尺寸封裝(WLCSP)是指在圓片狀態(tài)下完成再布線,凸點下金屬和焊錫球的制備,以及圓片級的探針測試,然后再將圓片進行背面研磨減薄

2023-05-06 09:06:41 1846

1846

FC-CSP 是芯片級尺寸封裝(CSP)形式中的一種。根據(jù)J-STD-012 標準的定義口,CSP 是指封裝體尺寸不超過裸芯片 1.2倍的一種封裝形式,它通過凸塊與基板倒裝焊方式實現(xiàn)芯片與基板的電氣

2023-05-04 16:19:13 2497

2497

半導體大規(guī)模生產(chǎn)過程中需要在晶圓上沉積集成電路芯片,然后再分割成各個單元,最后再進行封裝和焊接,因此對晶圓切割槽尺寸進行精準控制和測量,是生產(chǎn)工藝中至關(guān)重要的環(huán)節(jié)。

2023-04-28 17:41:49

封裝技術(shù)已經(jīng)不能滿足現(xiàn)狀。而隨著前端努力更好地縮小芯片尺寸,一個全新的技術(shù)領(lǐng)域出現(xiàn)了,那就是對先進封裝技術(shù)的重視。那么進口芯片是如何封裝的。進口芯片的封裝方法。下面安瑪科技小編為大家詳細講解。 對進口芯片進

2023-04-26 18:04:43 637

637

萊迪思憑借MachXO系列FPGA在控制功能方面長期處于領(lǐng)先地位。這些FPGA為當今數(shù)據(jù)中心、通信基礎(chǔ)設(shè)施和工業(yè)系統(tǒng)不斷增長的計算需求提供了理想的低功耗解決方案。

2023-04-25 14:46:52 207

207

萊迪思發(fā)布先進的系統(tǒng)控制FPGA - MachXO5T-NX繼續(xù)加強低功耗FPGA產(chǎn)品系列

2023-04-23 14:22:15 184

184 微產(chǎn)品封裝規(guī)格已近50種,品種超過7000個型號。在系統(tǒng)級封裝領(lǐng)域,晶導微已攻克了不少核心技術(shù),比如實現(xiàn)量產(chǎn)的反極性芯片制造工藝,掌握了高密度、低應力的IC框架設(shè)計以及專門針對多芯片引腳和PAD

2023-04-14 16:00:28

合封芯片是一種芯片封裝技術(shù),它將多個芯片通過引線相互連接在一起,形成一個更大的芯片結(jié)構(gòu),以便更好地實現(xiàn)集成和減小芯片尺寸。合封芯片的優(yōu)點是可以提高芯片的集成度和性能,同時可以減小芯片尺寸,從而提高芯片的功能密度和速度。

2023-04-11 14:09:04 989

989 ,封裝無需向芯片外擴展,使得WLP的封裝尺寸幾乎等于芯片尺寸。)

2.高傳輸速度(與傳統(tǒng)金屬引線產(chǎn)品相比,WLP一般有較短的連接線路,在高效能要求如高頻下,會有較好的表現(xiàn)。)

3.高密度連接(WLP可運用數(shù)組式連接,芯片

2023-04-06 17:50:56 0

0 wafer晶圓GDP703202DG恒流1mA表壓2Mpa裸片壓力傳感器die產(chǎn)品概述:GDP0703 型壓阻式壓力傳感器晶圓采用 6 寸 MEMS 產(chǎn)線加工完成,該壓力晶圓的芯片由一個彈性膜及集成

2023-04-06 14:48:12

在BGA封裝加持下,APM32F407IGH6芯片在擁有同系列產(chǎn)品的功能配置和相同引腳數(shù)情況下,具備更高的引腳密度及更大的引腳間距,將芯片尺寸控制在10mm x10mm小尺寸,大大縮小了芯片所占空間,并有助于提高芯片成品率。

2023-04-01 15:09:10 668

668 BOARD MACHXO2 SENSOR EXTENDER

2023-03-30 12:04:42

LPDDR-SDRAM CTRLR FOR MACHXO2

2023-03-30 12:02:09

LPDDR-SDRAM CTRLR FOR MACHXO2

2023-03-30 12:01:19

KIT DEVELOPMENT MACHXO2 PICO

2023-03-30 11:49:35

KIT DEVELOPMENT MACHXO2 PICO

2023-03-30 11:49:24

BOARD MACHXO2 IMAGE INTERFACE

2023-03-29 22:50:33

ADAPTER 256-BGA MACHXO2

2023-03-29 22:44:47

ADAPTER SOCKET MACHXO2 184CSBGA

2023-03-29 22:44:47

SOCKET ADAPTER MACHXO2 332CABGA

2023-03-29 22:44:43

ADAPTER 256-FTBGA MACHXO2

2023-03-29 22:44:42

ADAPTER FOR MACHXO2 64UCBGA

2023-03-29 22:44:38

SOCKET ADAPTER FOR MACHXO2 32QFN

2023-03-29 22:44:33

電子發(fā)燒友App

電子發(fā)燒友App

評論